# **Scaling of electronics**

Christer Svensson Linköping University, Sweden

Christer Svensson, QNANO workshop 2001

1

### Outline

Introduction

CMOS Logic

Physical limits to transistors and logic

Physical limits to interconnects

Conclusions

Christer Svensson, QNANO workshop 2001

### Introduction

Traditional logic techniques has been extremely successful (Moores law, 2x performance each 18 months, valid >30 years (as yet))

New techniques needed to prolong Moores law?

#### Objective:

Review "traditional logic" to put new techniques in perspective Investigate ultimate limits to "traditional logic"

Christer Svensson, QNANO workshop 2001

3

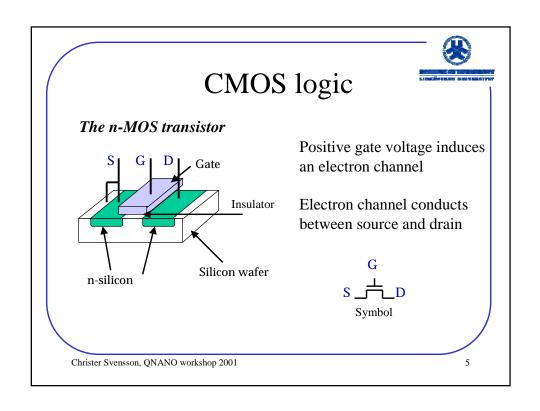

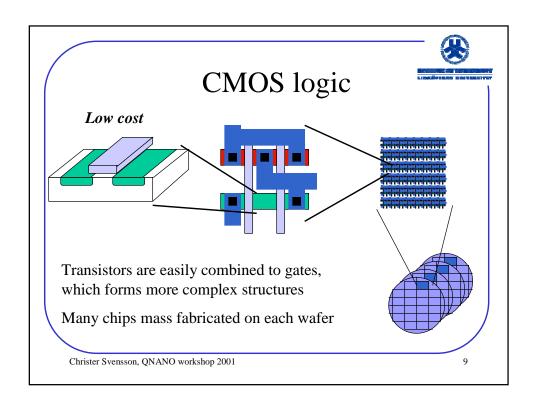

# **CMOS** logic

CMOS will be used as the main example of traditional logic (Wanless and Sah, 1963)

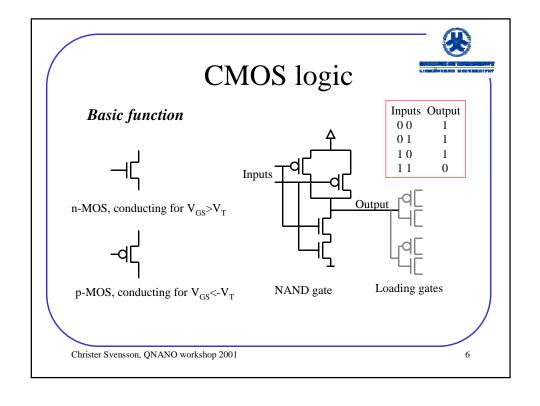

#### Key characteristics:

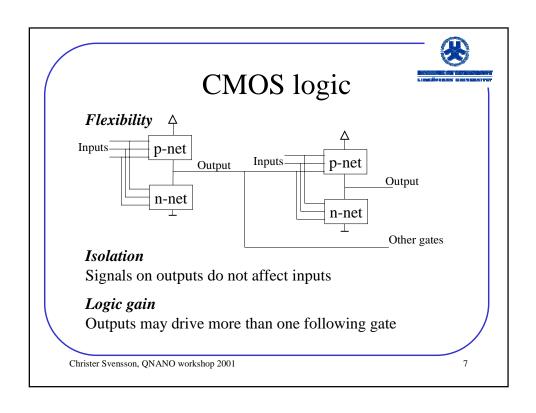

Flexibility (can form an infinite number of logic functions) Isolation (output does not affect input)

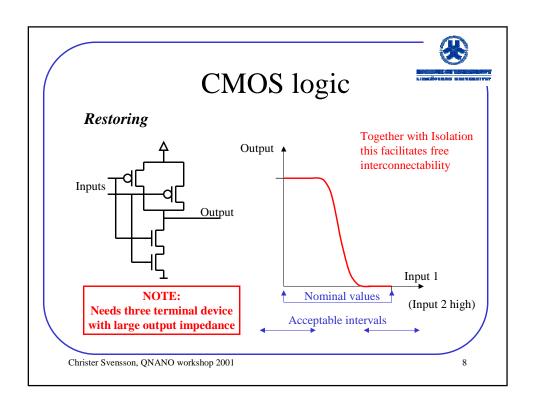

Logic gain (output may drive more than one following gate) Restoring (Signal quality restored in each gate)

Low cost

Speed

Low power consumption

Christer Svensson, QNANO workshop 2001

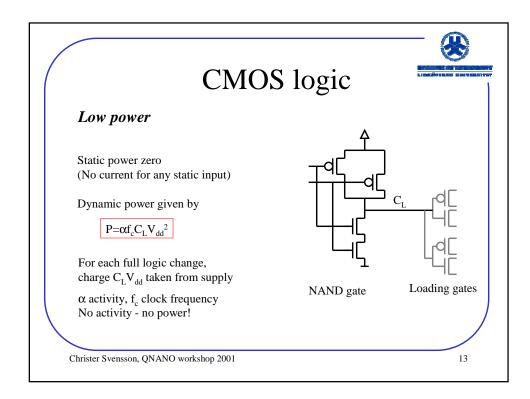

## **CMOS** logic

#### **CMOS** logic extremely robust:

0.1 - 250V supply voltage

4 - 600K operation temperature

0.1-20μm geometry

Facilitates mass produced chips with 100M simultaneously operating transistors.

Robert W Keyes, 2001: "The failure of any other [than vacuum tube and transistor] compact source of electronic gain to emerge in almost a century of electronics must be regarded as a fundamental limit to device technology"

Christer Svensson, QNANO workshop 2001

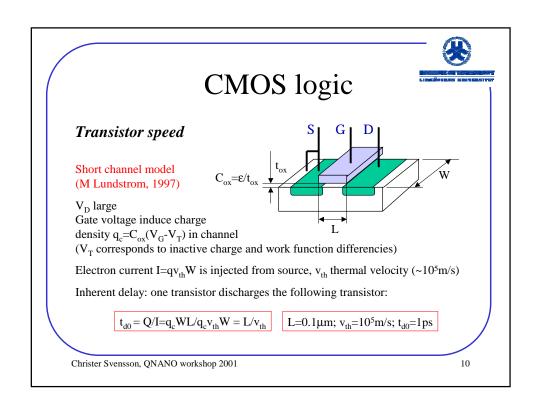

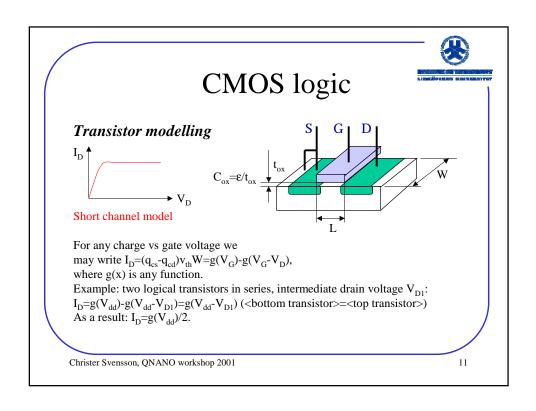

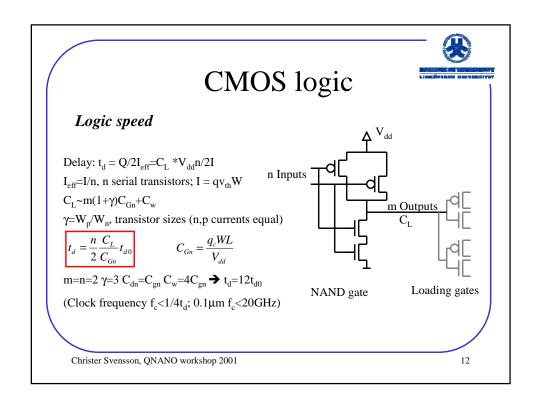

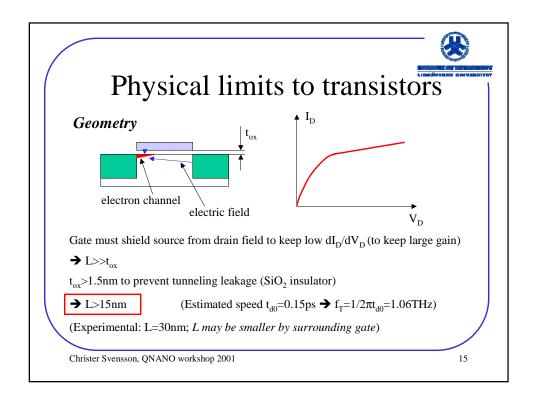

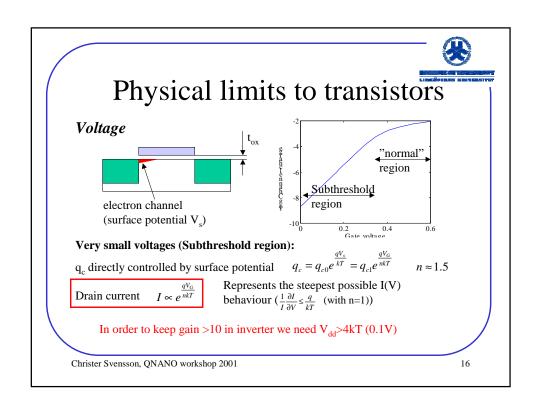

### Physical limits to transistors

#### Noise

Output node has a noise voltage of  $v_n^2$ =kT/C<sub>L</sub> (voltage variance) (Thermal noise in transistor channels at bandwidth given by channels and capacitor)

Assume  $P_{err} < 1/year; N=10^8; f_e=30 GHz \implies erfc \left(\frac{V_{dd}}{2v_n}\right) = 1.1 \cdot 10^{-26}$  (argument=7.56)

With  $\frac{V_{dd}^2}{4v_n^2} = \frac{C_L V_{dd}^2}{4kT}$  we get the a minimum stored energy  $C_L V_{dd}^2 = 1.3 \ 10^{-19} J = 0.8 eV$

Christer Svensson, QNANO workshop 2001

17

# Physical limits to transistors

#### The minimum gate

2-input, 2-output static CMOS gate with n-transisor L=15nm, W=30nm,  $t_{ox}$ =1.5nm

$$C_{Gn} \approx \frac{3.4 \cdot 10^{-11} \frac{L}{2} W}{w_{ox}} = 5aF$$

$C_L = 4*C_{Gn} = 20aF$

$V_{dd}$ =0.1V  $CV_{dd}^2$ =2  $10^{-19}$ J=1.25eV (close to noise limit!)

number of electrons: 12 (close to single electron!)

Christer Svensson, QNANO workshop 2001

# Physical limits to interconnects

**Electrical conductors have two limitations:**

**Signal velocity** limited by velocity of light,  $c = \frac{c_0}{\sqrt{\varepsilon}}$  (narrow wires worse; RC-limited)

**Data rate** limited by resistance, (A=metal cross section, L=wire length)  $B \approx B_0(\rho, \varepsilon, Z_0) \frac{A}{L^2}$

Wire limitations needs consideration, but is not a severe limitation to electronics inside chip or circuit board

(See C. Svensson, "Electrical interconnects revitalized", www.ifm.liu.se/~Christer/InterconnectManuscript.pdf)

Christer Svensson, QNANO workshop 2001

19

### Conclusions

Simple arguments can be used for understanding and predicting logic performance

Several key properties facilitates the ever-increasing complexity of CMOS logic

We are very far from fundamental limits today

- Moores law may be valid 20 years more (10000x increased performance)

- CMOS may approach fundamental physical limits

- These limits are most probably valid for any electronics-like system

Christer Svensson, QNANO workshop 2001

### References

R. W. Keyes, "Fundamental Limits of Silicon Technology", Proc. IEEE, Vol. 89, pp. 227-339, March 2001, and references therein.

Proc. IEEE, Special issue on The Limits of Semiconductor Technologiy, Vol. 89, No.3, March 2001.

M. Lundstrom, "Elementary Scattering Theory of the Si MOSFET", IEEE Electron Device Lett., pp. 361-363, July 1997.

R. Ohba and T. Mizuno, "Nonstationary Electron/Hole Transport in Sub-0.1 $\mu$ m MOS Devices: Correlation with Mobility and Low-Power CMOS Application", IEEE Tr. Electron Devices, Vol. 48, pp.338-343, Feb. 2001.

C. Svensson, "Electrical interconnects revitalized", unpublished, www.ifm.liu.se/~Christer/InterconnectManuscript.pdf

Christer Svensson, QNANO workshop 2001