# The 28 nm CMOS Power Amplifier

IECC 2017 Keynote talk 2017-05-19

Ted Johansson, Integrated Circuits and System, Dept. of Electrical Engineering, Linköping University, Sweden ted.johansson@liu.se

### Outline

- Moore's law

- Dennard scaling

- CMOS scaling beyond 130 nm

- Moore's law and radio circuit design

- The 28 nm CMOS Power Amplifier (PA)

- PA design in scaled CMOS for wireless applications

- FinFET and radio design

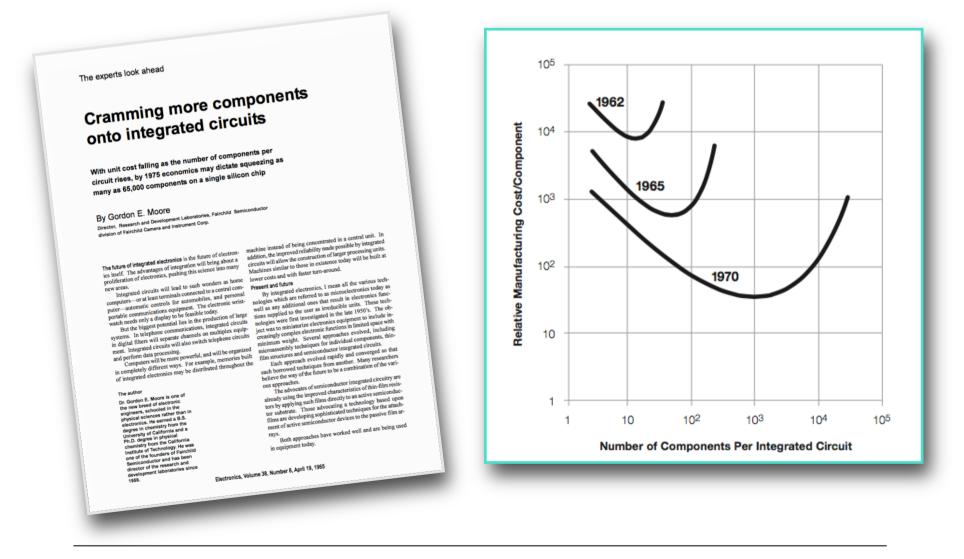

### Moore's law is not about scaling but economy!

3

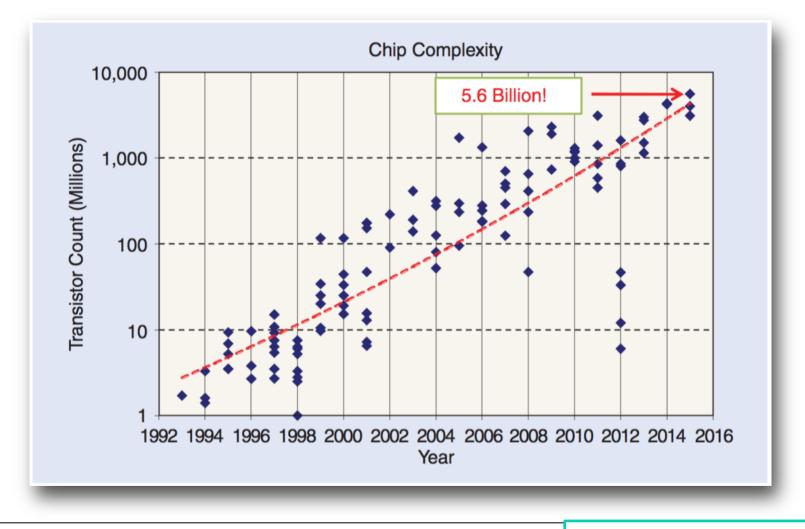

### Number of transistorer per chip

ISSCC 1970-2015: Doubling each 24 month

### Dennard scaling of MOS devices

| Component/circuit parameter   | Scaling factor*  |

|-------------------------------|------------------|

| Component dimension/thickness | 1/λ              |

| Doping concentration          | λ                |

| Gate oxide thickness          | 1/λ              |

| Supply voltage                | 1/λ              |

| Current                       | 1/λ              |

| Capacitance                   | 1/λ              |

| Delay time (1/speed)          | 1/λ              |

| Transistor power              | 1/λ²             |

| Energy efficiency ("MIPS/W")  | 1/λ <sup>3</sup> |

| Power density                 | 1                |

**Robert Dennard**

\* constant electrical field

Dennard et al., JSSC, pp. 256-268, Oct 1974 Dennard, SSC Mag, pp. 29-38, No. 2, 2015

### Dennard & Moore 1975-2000: The winning team!

<u>Dennard scaling</u> when transistors getting smaller:

- faster components and circuits,

- lower total power (constant power density),

- electronics can be made smaller, lighter, faster, better.

#### Moore's law:

- same cost per area when components scale,

- more transistors per chip,

- lower cost per transistor.

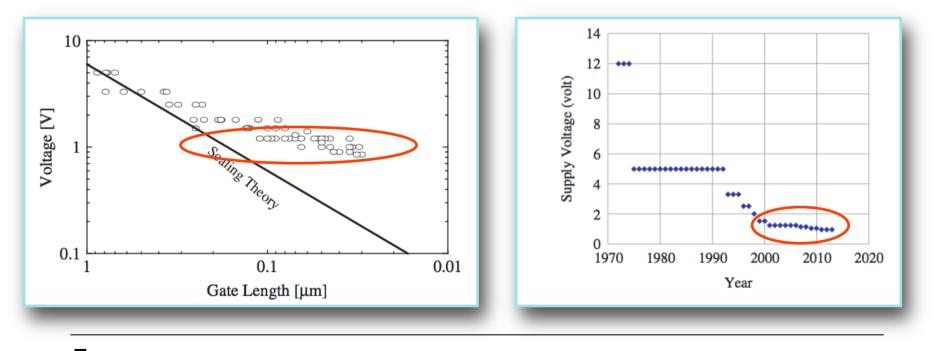

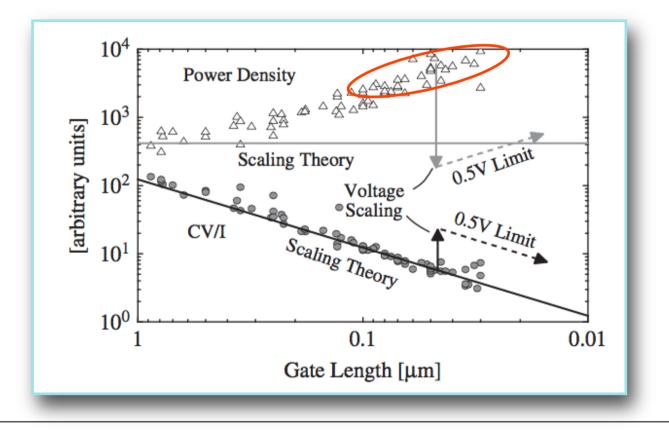

### Problem with Dennard scaling

- Supply voltage was not properly scaled, more like  $1/sqrt(\lambda)$ .

- Supply voltage reduction in practice stopped more than ten years ago.

- Thermal noise (kT/q = 25 mV at room temperature),

- Sub-threshold leakage (power consumption, thermal issues).

### Problem with Dennard scaling

- Power consumption limits the scaling

- Increased clock speed leads to higher power consumption

# CMOS scaling down to 130 nm was rather "linear"

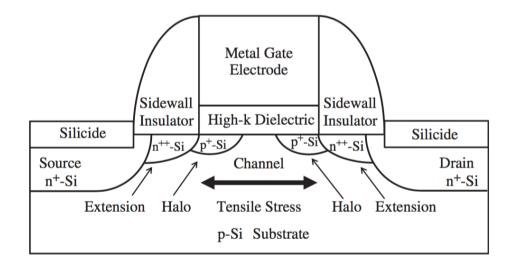

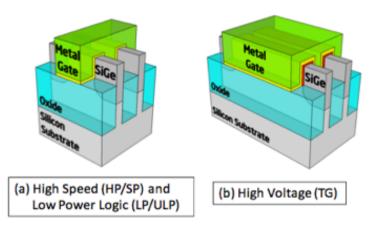

### 32/28 nm bulk MOSFET

90 nm: mechanical strain in the channel => higher mobility

90 nm: PD-SOI (reduced switching time, corresponding to one process node, but more higher substrate cost).

45 nm: Material with higher dielectric constants replacing SiO<sub>2</sub> as insulator in the gate (reduced leakage currents)

28 nm: Metal gate (smaller threshold voltage variations)

28 nm: FD-SOI Thin undoped channel with device properties given by vertical dimensions and backside bias.

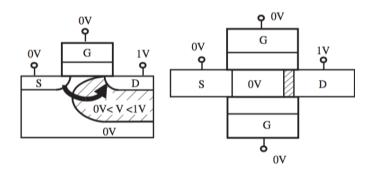

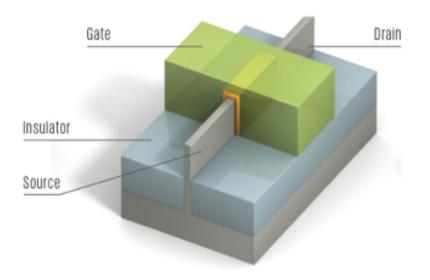

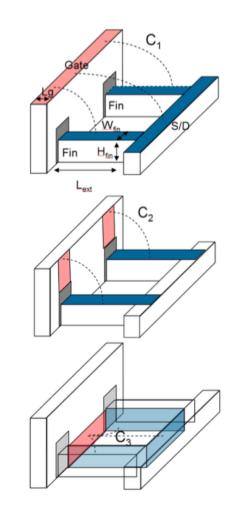

### 22 nm: Tri-Gate or FinFET

| FINFET ADVANTAGES      |                                                                                                         |  |

|------------------------|---------------------------------------------------------------------------------------------------------|--|

| PARAMETER              | DETAILS                                                                                                 |  |

| Power                  | Much lower power consumption allows high integration levels. Early adopters reported 150% improvements. |  |

| Operating voltage      | FinFETs operate at a lower voltage as a result of their lower threshold voltage.                        |  |

| Feature sizes          | Possible to pass through the 20nm barrier previously thought as an end point.                           |  |

| Static leakage current | Typically reduced by up to 90%                                                                          |  |

| Operating speed        | Often in excess of 30% faster than the non-<br>FinFET versions.                                         |  |

Intel 22 nm with extensions for SoC design (Jan et al., IEDM 2012)

First description? Hisamoto et al., TED 1991

### 2017: State-of-the-art is 10 nm

- Early 2015: Intel says 10 nm delayed until 2017 (ITRS=2015)

- April 2015: TSMC announced that 10 nm production would begin at the end of 2016.

- May 2015: Samsung Electronics showed off a 300 mm wafer of 10 nm FinFET chips.

- August 2016: Intel began trial production at 10 nm.

- October 2016: Samsung Electronics announced mass production at 10 nm.

- April 2017: Samsung started shipping their Galaxy S8 which uses Samsung's version of a 10 nm processor.

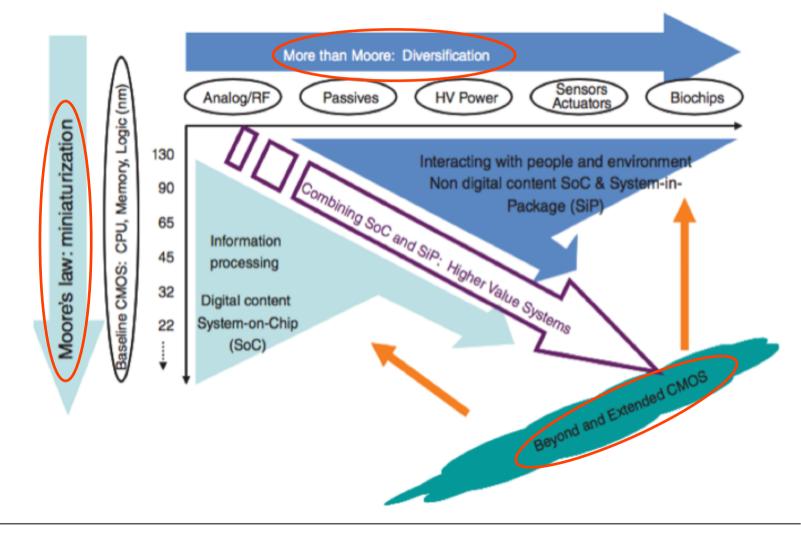

### Moore's law in several dimensions

### Moore's law and radio circuit design

- Nodes for many new radio circuit designs today is 28 nm on bulk substrate or FD-SOI. 40 and 55 nm also popular.

- Nodes give more than fast enough transistors for all wireless communication in the 1-6 GHz bands (mobile comm, wireless networks, sensors, etc.), but also for short range communication (e.g. 5G, 28 - 60 - 100+ GHz).

- Demands for high level of integration (of digital blocks) make the selected processes less suitable for radio design too small nodes - but we still have to live with this problem!

## The power amplifier (PA)

- Last active part in the transmitter before the antenna. Boosts the signal to higher power levels for transmitting the signal to a distant receiver.

- Power levels:

- Cellular phones: 23-24 Bm (Pav), up to 30 dBm (Ppeak),

- WLAN: up to 20-23 dBm (Pav), up to 30 dBm (Ppeak),

- Bluetooth: typically around 5 dBm.

- Frequency range often in the 1-6 GHz interval for CMOS integrated PAs

## The power amplifier (PA)

- Requirements for portable applications (consumer-oriented):

- high integration => low price,

- battery operation => high efficiency needed,

- high linearity => high data rate.

### How to reach high PA output power

Large devices (many parallel transistors) + impedance transformation. Power combination using (on-chip) transformers.

• High supply voltage

$$P = \frac{V^2}{2R}$$

"Digital" PAs (class-D inverter-based, using normal supply voltage)

### How to handle the high supply voltage?

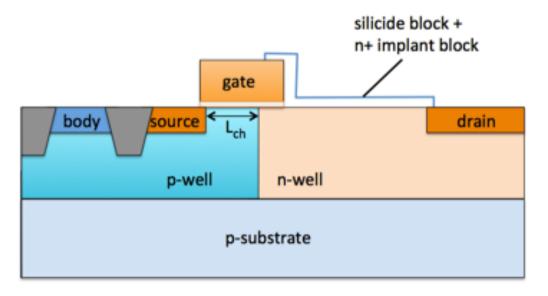

### New component/new structures

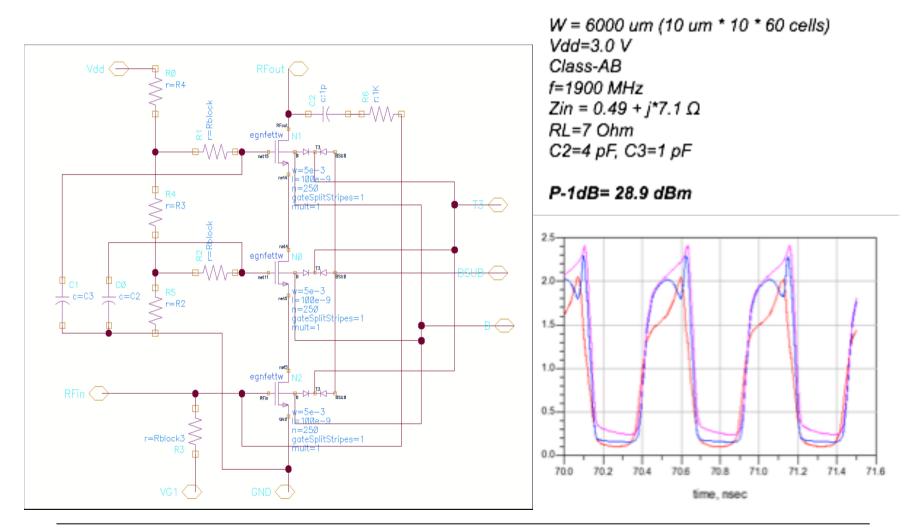

LDMOS structure with no additional process steps or masks  $^{\star}$

Designed in Global Foundry's 65 nm CMOS-process for WLAN applications. Concept scalable to (available in) 45 nm and 32/28 nm.

T. Johansson et al., EuMIC 2013

#### T. Johansson et al., EuMIC 2013

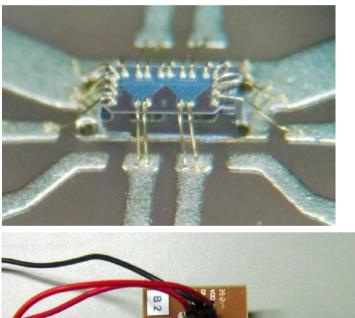

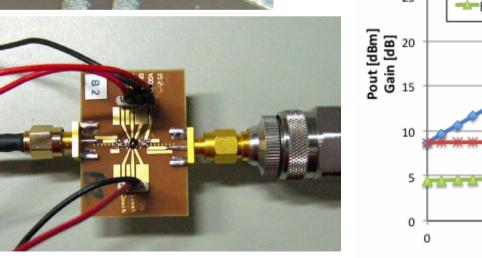

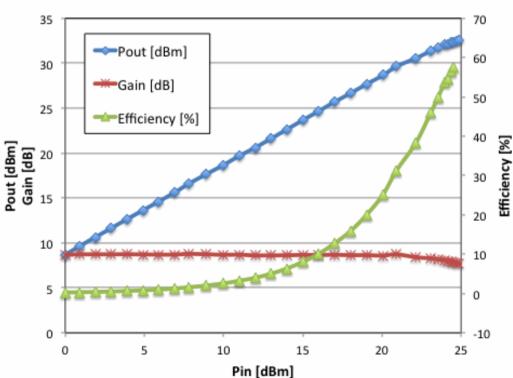

# WLAN PA

• Transistors with W=5.6 mm mounted on PCB

Differential PA, Vdd=3 V, f=2412 MHz **P-1dB = 32,5 dBm** (1,8 W). Class AB, efficiency over 50 % for unmodulated signal.

EDMOS f=2412 MHz

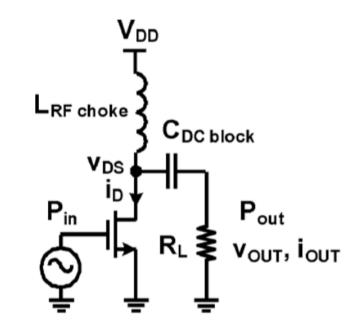

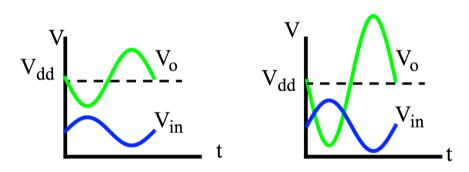

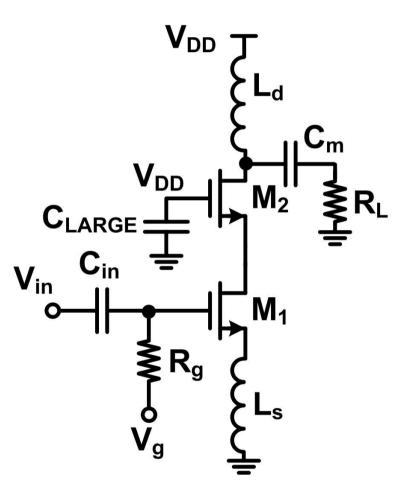

### The linear PA

- Linear PAs (class A, AB, ...) are the most commonly used amplifier classes on radio PA design.

- Drawback: 2 x supply over the drain node of the transistor.

How to handle the high voltage?

Most common circuit solution: **the cascode**

(stacked devices)

The voltage is however not evenly distributed between the transistors => not optimal (improved variants exist)

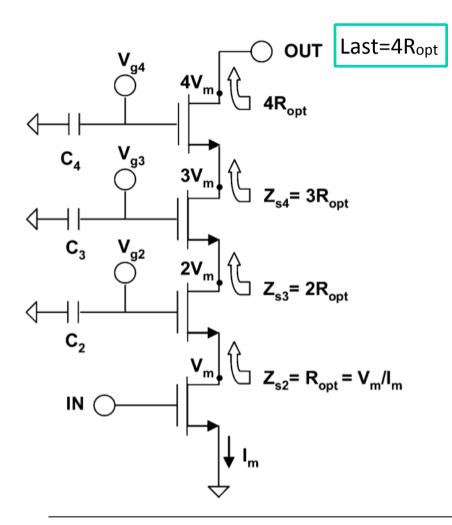

#### Transistor stacking: extending the concept

$C_{2}, C_{3}, C_{4} \text{ set } Z_{s2}, Z_{s3}, Z_{s4}$

$$Z_{\rm si} = \left(1 + \frac{C_{\rm gs}}{C_i}\right) \cdot \left(\frac{1}{g_m} \parallel \frac{1}{sC_{\rm gs}}\right)$$

$$\approx \left(1 + \frac{C_{\rm gs}}{C_i}\right) \cdot \frac{1}{g_m}, \quad \text{for } f_0 \ll F_t$$

In practice limited to four stacked devices

Chen et al., JSSC 2013

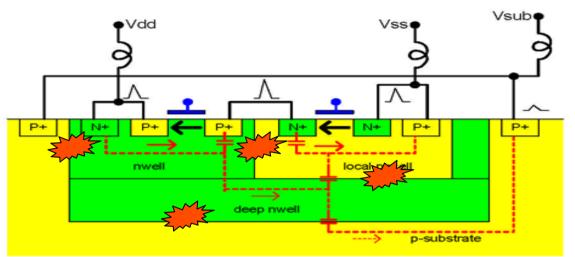

### Limitation for maximum supply voltage

- Conventional bulk CMOS: many diode breakdowns to wells and substrate.

- Scaled bulk CMOS: breakdown voltages down to 4-5 V.

- Stacked bulk components (PA): will be limited by the drainsubstrate breakdown of the uppermost transistor in the stack.

- With SOI, there is no breakdown to the substrate. Possible to stack components without breakdown voltage limitations.

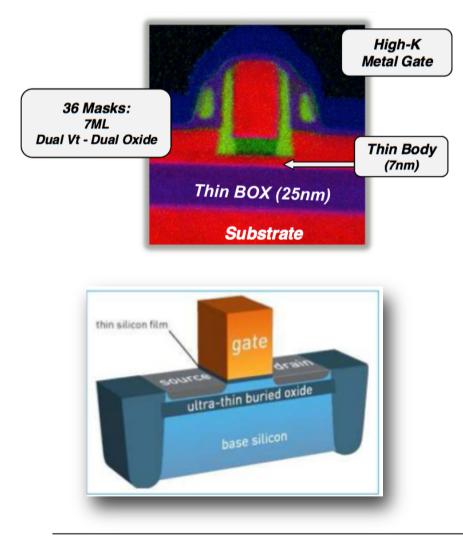

### 28 nm FD-SOI (UTBB)

L<sub>g</sub>=24 nm, T<sub>ox</sub>=1.8 nm, V<sub>sup</sub>=1.0 V ultra-thin silicon: 7 nm ultra-thin buried oxide: 25 nm

High-k dielectric Metal-gate electrode S/D: epitaxy raised Undoped channel Bulk/SOI integration

Stacked PA design: L<sub>g</sub>=150 nm, T<sub>ox</sub>=2.8 nm, V<sub>sup</sub>=1.8 V (+10 %)

**ST Microelectronics**

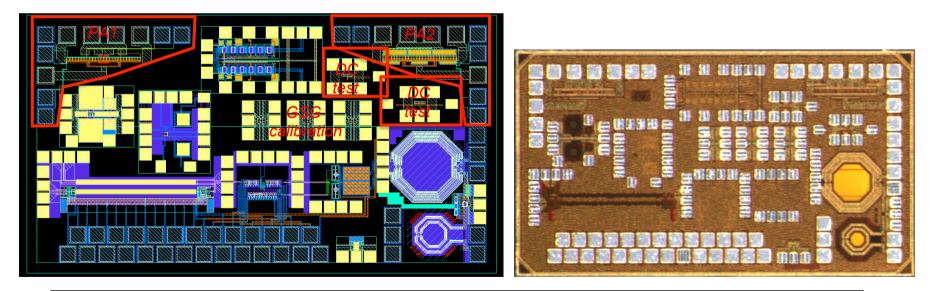

### 3-stacked high-power PA in 28 nm FD-SOI

### 3-stacked high-power PA in 28 nm FD-SOI

- Joint project Ericsson + Acreo Swedish ICT + LiU

- Area 1.5 x 2.2 mm

- Cost 50 k\$

- Under evaluation

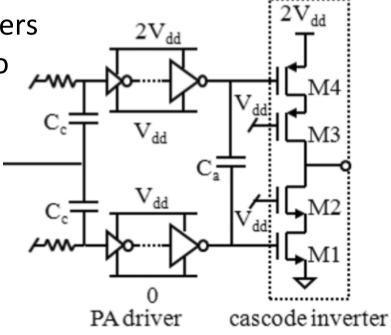

### "Digital PA"

- CMOS-inverters can be used as switched PA, class D.

- They operate at normal ("digital") supply voltage and has no over-voltage compared to other classes of PAs.

- In this particular case, the inverters are using a variant of cascode, so that the output stage can use 2 x V<sub>DD</sub>, resulting in higher output power.

Xu et al., JSSC, 2011

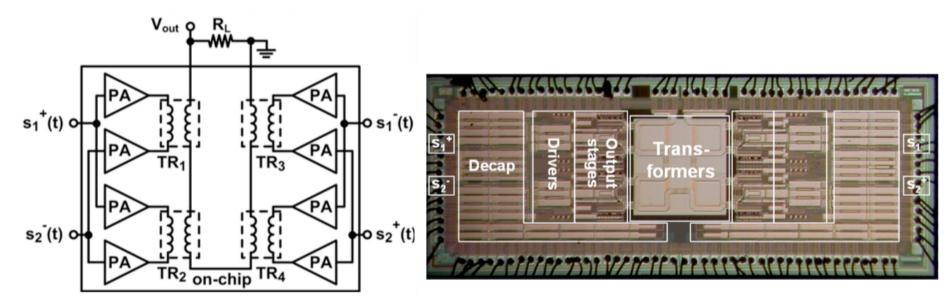

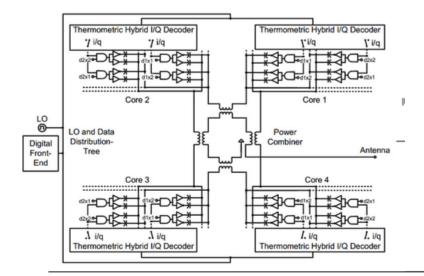

### "Digital PA" + transformer power combination

• The PAs are divided into 4 x differential PAs and power combined using an on-chip transformer.

4 x 1.5 mm, 130 nm CMOS

Fritzin et al., ESSCIRC 2011

### Hot topic!

#### ISSCC 2017 / SESSION 13 / HIGH-PERFORMANCE

#### 13.9 A 1.1V 28.6dBm Fully Integrated Digital Power Amplifier for Mobile and Wireless Applications in 28nm CMOS Technology with 35% PAE

Antonio Passamani<sup>1</sup>, Davide Ponton<sup>1</sup>, Edwin Thaller<sup>1</sup>, Gerhard Knoblinger<sup>1</sup>, Andrea Neviani<sup>2</sup>, Andrea Bevilacqua<sup>2</sup>

<sup>1</sup>Intel, Villach, Austria <sup>2</sup>University of Padova, Padova, Italy

|                            | This Work         |   |

|----------------------------|-------------------|---|

| Technology [nm]            | 28                |   |

| Supply voltage [V]         | 1.1               |   |

| Resolution [bit]           | 11                |   |

| Carrier Freq. [GHz]        | 2.5               |   |

| P <sub>sat</sub> [dBm]     | 28.6              |   |

| PAE @ P <sub>sat</sub> [%] | 35                |   |

| Modulation signal          | LTE 5-10MHz /     | ł |

|                            | WIFI 20-40MHz     |   |

| P <sub>avg</sub> [dBm]     | 20.7 / 17.3       |   |

| EVM [%]                    | 3.2-3.8 / 4.3-5.4 |   |

| PAE @ Pavg [%]             | 14.6 / 11         |   |

| ACLR [dBc]                 | -34.6/-44.7       |   |

| w/ DPD                     | No                |   |

| Area [mm <sup>2</sup> ]    | 1                 | Γ |

|                            |                   |   |

### FinFET and radio

- No recent examples in the literature of radio circuit demonstration using FinFETs (some at 45 nm node for pure research).

- Device simulation papers.

- Parasitic capacitances important!

- "similar characteristics in terms of transconductance, Early voltage, voltage gain, self-heating issue but UTBB outperforms FinFET in terms of <u>cutoff frequencies</u> thanks to their relatively <u>lower fringing parasitic capacitances.</u>" (Raskin, "FinFET versus UTBB SOI - a RF perspective", ESSDERC 2015)

### Summary

- Moore and Dennard: continued transistor scaling, currently at 10 nm for large processors

- FinFET for RFIC design: lot of parasitics make radio design unfavorable.

- Integrated radio design: 28 nm CMOS (bulk or FD-SOI) is "state-of-the-art".

- A lot of tricks needed to reach high output power (>= 30 dBm or 1W), but possible and with good enough performance for popular applications.

### Thank you for your attention!

www.liu.se