# A Tiny VHDL Guide

#### Petter Källström petter.kallstrom@liu.se

Version: 2.1

#### Abstract

This VHDL guide is aimed to show you some common constructions in VHDL, together with their hardware structure. It also tells the difference between concurrent and sequential VHDL code. The emphasize is on RTL level (synthesizable code).

# Contents

| 1        | Intr | oduction                        | 1 |

|----------|------|---------------------------------|---|

|          | 1.1  | A Simple Example                | 1 |

|          | 1.2  | RTL vs Behavioral VHDL          | 1 |

|          | 1.3  | Concurrent vs Sequential Syntax | 2 |

| <b>2</b> | Dat  | a Types                         | 3 |

|          | 2.1  | std_logic Based Data Types      | 3 |

| 3        | Dec  | larations and Definitions       | 3 |

|          | 3.1  | Use Package Declarations        | 3 |

|          | 3.2  | Entity Definitions              | 3 |

|          |      | Architecture Definitions        | 4 |

|          | 3.4  |                                 | 4 |

|          | 3.5  | Process Definitions             | 4 |

| <b>4</b> | Bas  | ic VHDL                         | 4 |

|          | 4.1  | Assignments                     | 4 |

|          | 4.2  | Logic Operations                  | 4 |

|----------|------|-----------------------------------|---|

|          | 4.3  | Arithmetic Operations             | 5 |

|          | 4.4  | Test Operations                   | 5 |

|          | 4.5  | Vectors and Indexing              | 5 |

| <b>5</b> | Con  | current Constructions             | 6 |

|          | 5.1  | When-Else: Multiplexer Net        | 6 |

|          | 5.2  | With-Select: One Hugh Multiplexer | 6 |

| 6        | Seq  | uential Constructions             | 7 |

|          | 6.1  | If-Then: "Multiplexer Net"        | 7 |

|          | 6.2  | Case-Is: "A Hugh Multiplexer"     | 7 |

| Aj       | open | dix A Misc Package Declarations   | 8 |

|          | A.1  | ieee.std_logic_1164               | 8 |

|          | A.2  | ieee.numeric_std                  | 8 |

# 1 Introduction

This document is a very brief VHDL summary, intended as a simple non-covering help during the labs.

#### 1.1 A Simple Example

A simple example of a VHDL file is depicted in Code 1.

- library, use ieee.std\_logic\_1164.all; ⇒ Access the standard types and functions defined in VHDL.

- entity port(...); end entity;  $\Rightarrow$  Defines the "public interface".

- **std\_logic**  $\Rightarrow$  "*The*" data type for digital logic. Mostly '0' or '1'.

- architecture ... end architecture  $\Rightarrow$  The "engine".

- **RTL** stands for "Register Transfer Level".

- signal foo : std\_logic;  $\Rightarrow$  Declares an internal signal.

- $\operatorname{process}(\operatorname{clk})$ ,  $\operatorname{rising\_edge}(\operatorname{clk}) \Rightarrow$  Generates the D-flip-flop.

- foo  $\leq$  a and b;  $\Rightarrow$  The AND gate, assigned to the DFF.

- $\mathbf{y} \leq \mathbf{foo}; \Rightarrow \text{direct connection.}$

#### 1.2 RTL vs Behavioral VHDL

VHDL can, in some sense, be divided into **RTL** and **behavioral** code.

library ieee; use ieee.std\_logic\_1164.all; -- this is a comment entity and\_dff is port(clk : in std\_logic; a,b : in std\_logic; y : out std\_logic); end entity; architecture rtl of and\_dff is signal foo : std\_logic; begin process(clk) begin if rising\_edge(clk) then foo  $\leq$  a and b; end if; end process; y <= foo; end architecture;

Code 1: A simple VHDL example.

## 1.2.1 RTL VHDL

RTL ("Register Transfer Level") code can be directly synthesized into hardware, in terms of gates, registers etc.

## 1.2.2 Behavioral VHDL

Behavioral VHDL is used for simulation only. In addition to what can be described as RTL code, it can use much more complex constructions, e.g. file access.

#### 1.3 Concurrent vs Sequential Syntax

VHDL code can, in some sense, be divided into concurrent and sequential code.

By default, the code in the architecture is concurrent. Each statement corresponds to a hardware block. You can have processes, and within those, the code is sequential.

#### 1.3.1 Concurrent VHDL

Concurrent VHDL will always generate combinational logic.

Code 2 shows three ways of writing the logic net in (d). The intermediate signal x is not defined in (c).

| x <= a or b;<br>y <= x and c; |     | $y \leq (a \text{ or } b) \text{ and } c;$ | $ \begin{array}{c} a \longrightarrow \geq 1 \\ b \longrightarrow \geq 1 \\ c \longrightarrow & k \end{pmatrix} \rightarrow y $ |

|-------------------------------|-----|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| (a)                           | (b) | (c)                                        | (d)                                                                                                                            |

Code 2: Some examples of the same thing.

#### 1.3.2 Sequential VHDL

Use processes to generate registers, DFFs etc. The code in the process is understandable if you think it as a sequential execution, that starts on the clock edge, and where all assignments are updated when the "execution" is done. Versions (a) and (b) in Code 3 gives the behavior depicted in (c).

| <pre>process(clk) begin<br/>if rising_edge(clk) then<br/>x &lt;= a or b; (1)<br/>y &lt;= x and c; (2)<br/>end if;<br/>end process;</pre> | <pre>process(clk) begin if rising_edge(clk) then y &lt;= x and c; (2) x &lt;= a or b; (1) end if; end process;</pre> | $a \xrightarrow{(1)} x \xrightarrow{(2)} y$ $c \xrightarrow{(1)} x \xrightarrow{(2)} y$ $c \xrightarrow{(1)} y$ |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| (a)                                                                                                                                      | (b)                                                                                                                  | (c)                                                                                                             |

Code 3: Two ways of writing the same thing. Note that c is "AND:ed" with the *old* version of (a OR b).

# 2 Data Types

There are some data types in VHDL that is good to know about.

# 2.1 std\_logic Based Data Types

The package ieee.std\_logic\_1164 contains the data type std\_logic, and a set of operations on this, and some derived data types from this, e.g., std\_logic\_vector.

## 2.1.1 std\_logic

The type std\_logic has binary values, as '0', '1' or '-' (don't care).

## $2.1.2 \ std\_logic\_vector$

A std\_logic\_vector is an array of std\_logic. It must have non-negative indices. The array spans from left to right, and the index can be increasing or decreasing, e.g. (0 to 2) or (5 downto 1).

Constants are given as "1001". Hexadecimal constants can be written as X"a3".

The packages ieee.std\_logic\_signed and ieee.std\_logic\_unsigned contains arithmetic operations on those.

## 2.1.3 signed, unsigned

The package ieee.numeric\_std declares the data types SIGNED and UNSIGNED, both have the same definition as std\_logic\_vector. They are treated as unsigned and two's complement signed number respectively.

# 3 Declarations and Definitions

## 3.1 Use Package Declarations

Some examples:

- library ieee; Declares that we want to access the entire content defined by ieee.

- use ieee.std\_logic\_1164.all; We want simple access to all declarations in the package.

- use ieee.std\_logic\_unsigned.CONV\_INTEGER; Simplified access to CONV\_INTEGER.

- use ieee.std\_logic\_signed."+"; The "+" operator (e.g. a + b).

Without the use command, you can access the "+" operator as ieee.std\_logic\_signed."+"(a,b) instead of "a+b".

You can find a good list of the standard packages, and what they contains on the web page [1], and in App A.

# 3.2 Entity Definitions

The entity describes the module I/O pins. The definition usually looks like:

entity {ename} is port({plist}); end entity;

- $\{\underline{\text{ename}}\} \Rightarrow$  The name of the entity.

- {plist}  $\Rightarrow$  A list of design "pins", on the form "a1,a2,... : {dir} typeA; b1,b2,... : {dir} typeB; ...".

- {dir} ⇒ the direction of the pins. Typically in or out. You can read from (but not write to) an in pin. You can write to (but not read from) an out pin.

#### 3.3 Architecture Definitions

The architecture is like the engine. The syntax for the architecture definition is

architecture  $\{\underline{aname}\}$  of  $\{\underline{ename}\}$  is  $\{\underline{declarations}\}$  begin  $\{body\}$  end architecture;

- $\{\underline{\text{aname}}\} \Rightarrow \text{The name of the architecture, e.g., rtl.}$

- $\{\underline{\text{ename}}\} \Rightarrow$  The name of the entity it implements.

- $\{\underline{\text{declarations}}\} \Rightarrow \text{Declare/define signals, functions, aliases, constants, component etc. here.}$

- $\{body\} \Rightarrow$  Here is the body of the architecture the logic definition.

#### 3.4 Signal Declarations

Signals are declared before the begin in the architecture. It can look like in Code 4.

```

architecture rtl of foo is

signal sl1,sl2 : std_logic; -- two signals of type std_logic

signal sl3 : std_logic := '0'; -- initiates to '0'

signal slv1 : std_logic_vector(7 downto 0); -- a byte.

signal slv2 : std_logic_vector(11 downto 0) := X"3ff"; -- initial value = 1023.

begin

```

Code 4: Examples of signal declaration.

#### 3.5 Process Definitions

A process is placed in the concurrent code, and contains sequential code.

$\{\underline{pname}\}$  : process( $\{\underline{sensitivity \ list}\}$ ) begin  $\{\underline{body}\}$  end process;

- {pname} :  $\Rightarrow$  An optional name of the process.

- {sensitivity list} ⇒ A list of signals that should "trig the process to start". Most often just (clk), or (clk,reset).

- $\{body\} \Rightarrow$  The sequential code.

# 4 Basic VHDL

What is stated here holds in both concurrent and sequential VHDL.

#### 4.1 Assignments

The "<=" operator is used to assign signals.

## 4.2 Logic Operations

Those operations works typically on std\_logic, and element wise on std\_logic\_vector.

- not

- and, nand

- or, nor

- xor, xnor

Example of a multiplexer implemented with logic gates:

res <= (a0 and not s) or (a1 and s);

## 4.3 Arithmetic Operations

You can use arithmetic operations like a+b, a-b, -a or a\*b.

Those operations works on numerical data types, like  $std_logic_vector$ , signed or unsigned. When used on  $std_logic_vector$ , the functions are available in the packages ieee. $std_logic_unsigned$  and ieee. $std_logic_signed$ , that might behave differently (since, e.g. "1011" is -5 in a signed system, and +11 in an unsigned system).

## 4.4 Test Operations

Those operates on numerical data types. The operations returns the data type boolean, used by, e.g. if statements.

- =, /=  $\Rightarrow$  Equal or not equal. Those also works on std\_logic.

- <, <=  $\Rightarrow$  Less than (or equal).

- >, >=  $\Rightarrow$  Greater than (or equal).

Note that the operator <= is also an assignment operator.

## 4.5 Vectors and Indexing

VHDL have great support for vectors, e.g. std\_logic\_vector.

We use the signals in Table 1 to exemplify the operations.

| Signal                                           | Signal Type                       |          |  |

|--------------------------------------------------|-----------------------------------|----------|--|

| x,y                                              | std_logic                         | 'x', 'y' |  |

| an                                               | an std_logic_vector(n-1 downto 0) |          |  |

| bn                                               | $b_{n-1} \dots b_0$ "             |          |  |

|                                                  | Examples                          |          |  |

| a4 std_logic_vector(3 downto 0) " $a_3a_2a_1a_0$ |                                   |          |  |

Table 1: Declaration of signals used in examples.

#### 4.5.1 Vector Indexing

Indexing is illustrated by the examples in Table 2.

| Expression              | Result                               |

|-------------------------|--------------------------------------|

| a4(2)                   | ' $a_2$ ', a std_logic               |

| a4(2 downto 2)          | " $a_2$ ", a vector with one element |

| a4(2 downto 3)          | "", a vector with zero elements      |

| a4(3 downto 2)          | "a <sub>3</sub> a <sub>2</sub> "     |

| a5(3 downto 2) <= "10"; | $a5 = "a_4 10 a_1 a_0"$              |

Table 2: Examples of vector indexing.

#### 4.5.2 Vector concatenation

The "&" operator is used to merge vectors, and works for both std\_logic and std\_logic\_vectors. The result is always a vector. Some examples are shown in Table 3

| Expression             | Result                                                                                                            |

|------------------------|-------------------------------------------------------------------------------------------------------------------|

| x & y;                 | " <i>xy</i> "                                                                                                     |

| a3 & b4                | $a_2a_1a_0b_3b_2b_1b_0$ "                                                                                         |

| x & b3                 | " <i>xb</i> <sub>2</sub> <i>b</i> <sub>1</sub> <i>b</i> <sub>0</sub> "                                            |

| b5(0) & b5(4 downto 1) | " <i>b</i> <sub>0</sub> <i>b</i> <sub>4</sub> <i>b</i> <sub>3</sub> <i>b</i> <sub>2</sub> <i>b</i> <sub>1</sub> " |

| a5 <= ('0' & b4) + '1' | " $a_4a_3a_2a_1a_0$ ", where $a_{30} = b4+1$ , $a_4 = carry$ out.                                                 |

Table 3: Examples of vector concatenation

#### 4.5.3 Aggregation: The "(others=>'0')" Syntax

In assignments, you can fill the target signal with, e.g., zeros, by a5 <= (others=>'0');

#### 4.5.4 Shifting

The easiest way of shifting is to use a combination of aggregation and indexing, as in Table 4.

| Example                           | Result                         | Operation                             |

|-----------------------------------|--------------------------------|---------------------------------------|

| x & b5(4 downto 1);               | $"xb_4b_3b_2b_1"$              | shift in x from left (right shift).   |

| b5(3 downto 0) & x;               | $"b_3b_2b_1b_0x"$              | shift in x from right (left shift).   |

| a5 <= b5(4) & b5(4 downto 1);     | a5 = " $b_4 b_4 b_3 b_2 b_1$ " | arithmetic shift right.               |

| b5(3 downto 0) <= b5(4 downto 1); | b5 = " $b_4b_4b_3b_2b_1$ "     | arithmetic shift right <sup>1</sup> . |

<sup>1</sup> This should be performed in a process, or  $b_0 = b_1 = b_2 = b_3 = b_4$ , e.g. just a wire with five names.

Table 4: Shift operators for the bit\_vector data type.

# 5 Concurrent Constructions

Concurrent VHDL statements are "executed" continuously, and corresponds to combinational logic.

## 5.1 When-Else: Multiplexer Net

The syntax for the when else assignment is

$\{\underline{\text{res}}\} \leq \{\underline{\text{val1}}\}\ \text{when}\ \{\underline{\text{cond1}}\}\ \text{else}\ \{\underline{\text{val2}}\}\ \text{when}\ \{\underline{\text{cond2}}\}\ \text{else}\ \dots\ \text{else}\ \{\underline{\text{valN}}\};$

If  $\{\underline{\text{cond1}}\}$  is true, then  $\{\underline{\text{res}}\}$  is assigned the value  $\{\underline{\text{val1}}\}$ . Otherwise  $\{\underline{\text{cond2}}\}$  is tested, and so on. If no  $\{\underline{\text{condn}}\}$  is true,  $\{\underline{\text{valN}}\}$  is used. See example in Code 5.

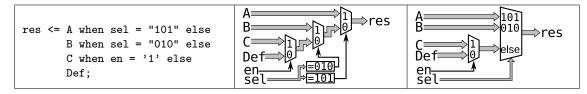

Code 5: When-else: A multiplexer net, in VHDL and as a schematic (before and after optimization).

## 5.2 With-Select: One Hugh Multiplexer

The syntax for the With-Select statement is

with  $\{expr\}\$  select  $\{\underline{res}\}\$  <=  $\{\underline{val1}\}\$  when  $\{\underline{choice1}\}\$ ,  $\{\underline{val2}\}\$  when  $\{\underline{choice2}\}\$ , ...  $\{\underline{valN}\}\$  when others;

- If  $\{expr\} = \{\underline{choice1}\}$ , then  $\{\underline{res}\}$  is assigned the value  $\{\underline{val1}\}$ .

- Otherwise  $\{expr\} = \{\underline{choice2}\}$  is tested, and so on.

- If  $\{\exp\}\neq\{\underline{choicen}\}, n = 1, 2, \dots, (N-1), \text{ then } \{\underline{valN}\}$  is used.

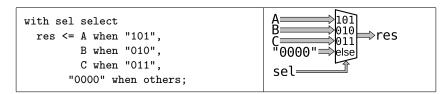

Code 6: With-select: One big multiplexer, in VHDL and as a schematic.

# 6 Sequential Constructions

In sequential VHDL, the signal assignments are made to the input of DFFs/regs. If a signal is not assigned during a clock cycle, it will keep it's value (by pulling the **en** signal to the DFF/reg low).

# 6.1 If-Then: "Multiplexer Net"

The if statement works like in any programming language. The syntax is:

if  $\{\underline{\text{cond1}}\}$  then  $\{\underline{\text{stats1}}\}$  elsif  $\{\underline{\text{cond2}}\}$  then  $\{\underline{\text{stats2}}\}$  elsif ...else  $\{\underline{\text{statsN}}\}$  end if;

- $\{\underline{\text{cond}n}\}, n = 1, 2, \dots, N \Rightarrow \text{Conditions of type boolean.}$

- $\{\underline{\text{statsn}}\}, n = 1, 2, \dots, (N 1) \Rightarrow$  Statements that should be "executed".

- elsif  $\ldots$  then  $\Rightarrow$  Optional.

- else  $\Rightarrow$  Optional.

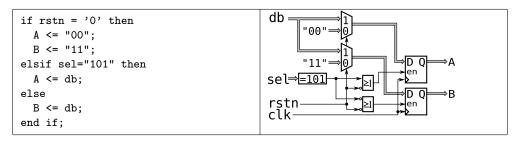

Code 7: An if-then statement, and it corresponding net.

## 6.2 Case-Is: "A Hugh Multiplexer"

The case-is construction have the syntax:

case  $\{expr\}$  is when  $\{\underline{choice1}\} \Rightarrow \{\underline{stats1}\}$  when  $\{\underline{choice2}\} \Rightarrow \dots$  when others  $\Rightarrow \{\underline{statsN}\}$  end case;

- $\{\exp \} \Rightarrow$  Signal or expression to test against.

- { $\underline{\text{choicen}}$ },  $n = 1, 2, \dots, (N 1) \Rightarrow$  Constant values to compare with {expr}.

- $\{\underline{\text{stats}n}\}, n = 1, 2, \dots, N \Rightarrow \text{Statements to execute.}$

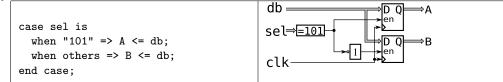

Code 8: A case-is statement, with corresponding net.

# References

$[1] \ \texttt{http://www.csee.umbc.edu/portal/help/VHDL/stdpkg.html}$

#### Misc Package Declarations Appendix A

This appendix aims to give a quick-and-sloppy overview of some ieee packages. They are explained more in details in [1].

#### Notations in this appendix:

- sl  $\Rightarrow$  std\_logic.

- $S \Rightarrow$  signed.

- $slv \Rightarrow std_logic_vector.$

- $U \Rightarrow unsigned.$ • US  $\Rightarrow$  U or S.

- int  $\Rightarrow$  An integer (e.g. 48).

#### A.1ieee.std\_logic\_1164

The "standard" package for synthesizable code. Types

- std\_logic  $\Rightarrow$  {'U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-'}.

- std\_logic\_vector  $\Rightarrow$  array of std\_logic.

- ...and more.

## **Functions**/operators

- not sl. • sl aox sl.

- not slv. • slv aox slv.

#### A.2ieee.numeric\_std

Contains the definitions of the types SIGNED and UNSIGNED, and the operators on those. Types

• SIGNED, UNSIGNED  $\Rightarrow$  identical definition as slv, but own types.

## **Functions**/operators

- U+U, S+S, +US, U-U, S-S, -S

- U\*U, S\*S.

- abs S.

- RESIZE(US, int).

- not U, not  $S \Rightarrow$  bitwise not.

- TO\_INTEGER(US)  $\Rightarrow$  S  $\rightarrow$  int, U  $\rightarrow$  nat.

- TO\_UNSIGNED(int, int)  $\Rightarrow$  2nd arg = size.

- TO\_SIGNED(int, int).

- $U_{\searrow \neq}^{\le =} U, S_{\searrow \neq}^{\le =} S, US_{>\neq}^{\le =} int, int_{>\neq}^{\le =} US$

- U aox U, S aox S  $\Rightarrow$  logic operators.

- STD\_LOGIC\_VECTOR(...), UNSIGNED(...), SIGNED(...)  $\Rightarrow$  convert between S, U and slv.

•  $\leq = \\ >\neq \Rightarrow <, <=, =, /=, >= \text{ or } >.$ •  $aox \Rightarrow and, or, xor, nand,$ nor or xnor.

• rising\_edge(sl).

• falling\_edge(sl).